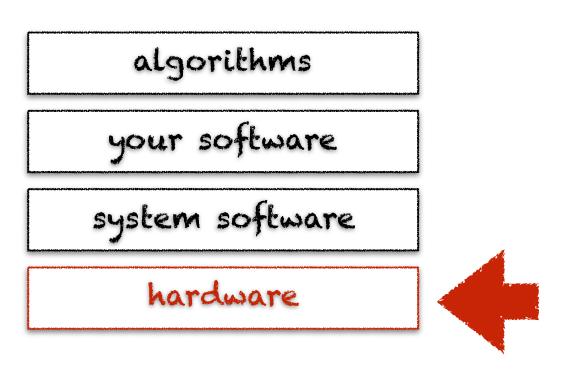

# computer architecture

# learning objectives

- understand the basics of how a computer works

- + understand the basics of binary computation

- + learn the basics of the Von Neumann architecture

# what's a computer?

hardware

so-ftware

### mathematics

a dual origin

Associative Rules:

$$(p \land q) \land r \Leftrightarrow p \land (q \land r)$$

$$p \land (q \lor r) \Leftrightarrow (p \land q) \lor (p \land r)$$

Distributive Rules:

$$p \land (q \lor r)$$

Idempotent Rules:  $p \land p \Leftrightarrow p$

$$(p \wedge q) \wedge r \Leftrightarrow p \wedge (q \wedge r)$$

$$\frac{(p \land (q) \land r)}{p \land (q \lor r)} \Leftrightarrow (p \land q) \lor (p \land r)$$

$$\neg \neg p \Leftrightarrow p$$

$$\neg (p \land q) \Leftrightarrow \neg p \lor \neg q$$

$$p \wedge q \Leftrightarrow q \wedge p$$

$$p \lor (p \land q) \Leftrightarrow p$$

$$\begin{array}{ccc}

p & \langle p & \langle q & \rangle \\

p & \rangle & F \Leftrightarrow F & p & \wedge T \Leftrightarrow p

\end{array}$$

$$p \wedge (\neg p) \Leftrightarrow F$$

$$(p \lor q) \lor r \Leftrightarrow p \lor (q \lor r)$$

$$(p \lor q) \lor r \leftrightarrow r$$

$$p \lor (q \land r) \Leftrightarrow (p \lor q) \land (p \lor r)$$

$$p \lor p \Leftrightarrow p$$

$$\neg (p \lor q) \Leftrightarrow \neg p \land \neg q$$

$$p \lor q \Leftrightarrow q \lor p$$

$$p \land (p \lor q) \Leftrightarrow p$$

$$p \land (p \lor q) \qquad p \lor F \Leftrightarrow p$$

$$p \lor T \Leftrightarrow T \qquad p \lor F \Leftrightarrow p$$

$$p \lor (\neg p) \Leftrightarrow T$$

$$rac{p}{F} = rac{q}{F} = rac{p}{V} = rac{q}{V} = ra$$

$$\left\{\frac{2^{i}-1}{2^{i}}\right\}_{i=1}^{\infty} = \frac{1}{2}, \frac{3}{4}, \frac{7}{8}, \frac{15}{16}, \dots,$$

$$\left\{\frac{n+1}{n}\right\}_{i=1}^{\infty} = \frac{2}{1}, \frac{3}{2}, \frac{4}{3}, \frac{5}{4}, \dots$$

#### electronics

$\frac{a_{n+1}}{a_n} = \frac{(n+1)!}{(n+1)^{n+1}} \frac{n^n}{n!} = \frac{(n+1)!}{n!} \frac{n^n}{(n+1)^{n+1}} = \frac{n+1}{n+1} \left(\frac{n}{n+1}\right)^n = \left(\frac{n}{n+1}\right)^n < 1.$

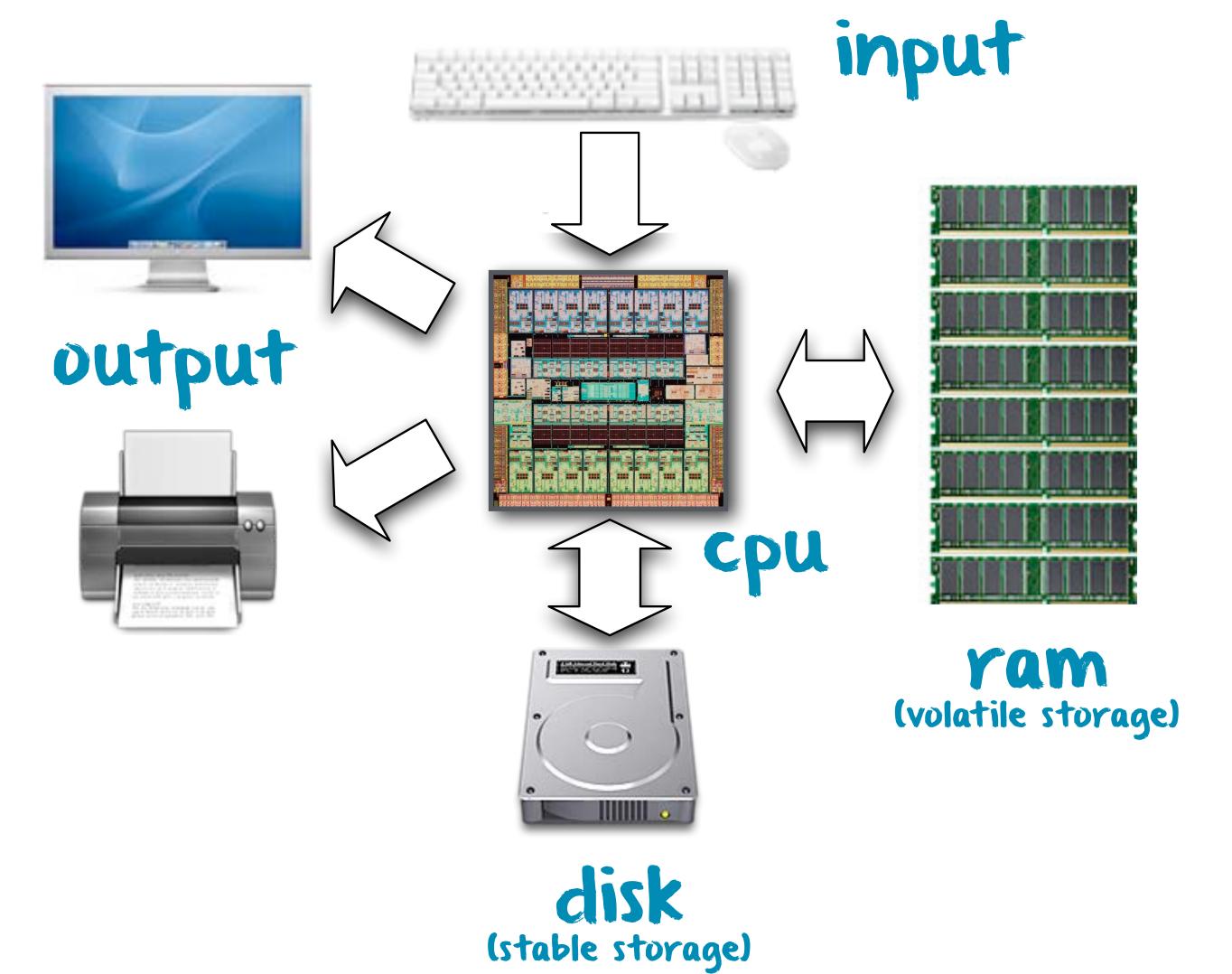

# what's hardware?

cpu = central processing unit

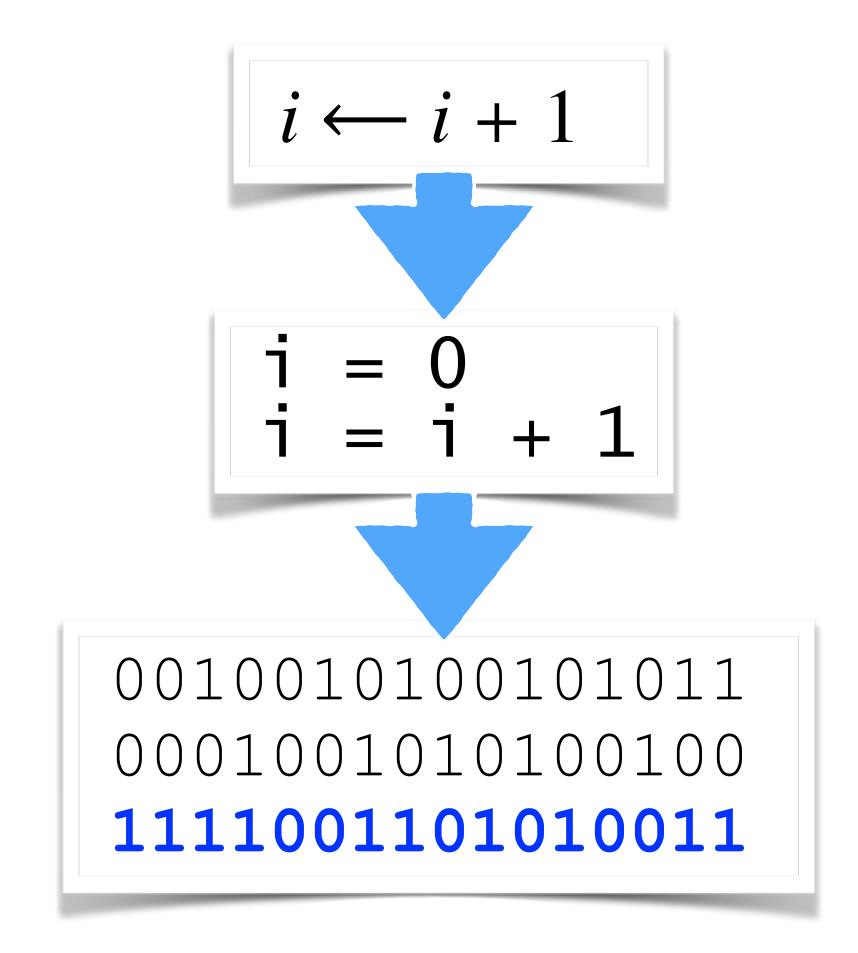

# what's software?

we will come back to these transformations in the next module

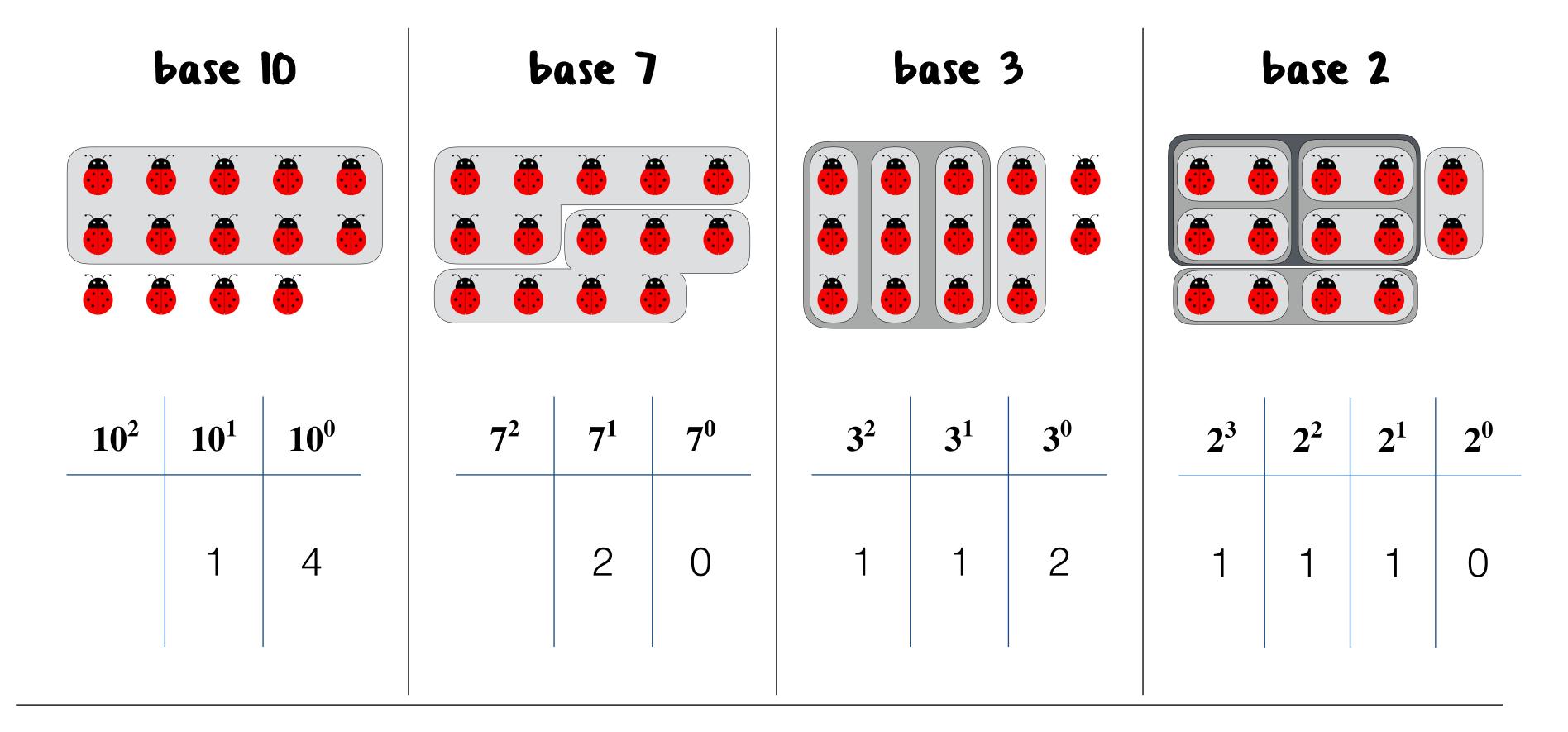

# binary computation

note that in a computer, binary words are not only used to represent integer numbers

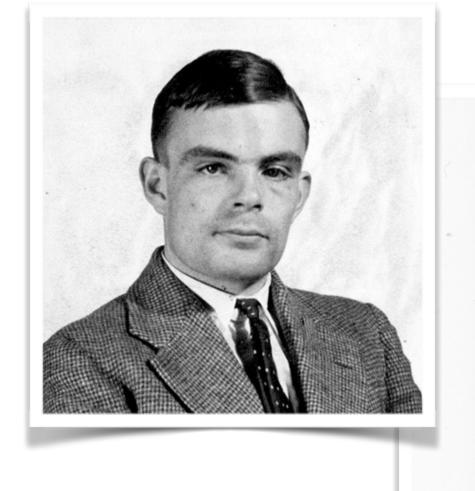

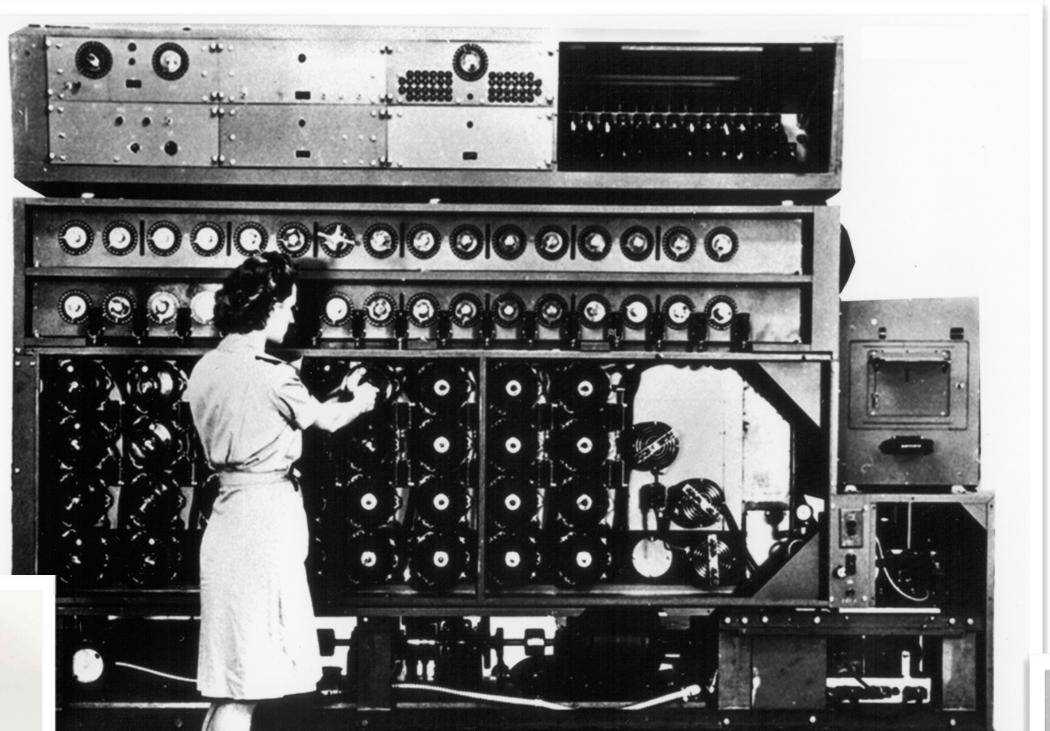

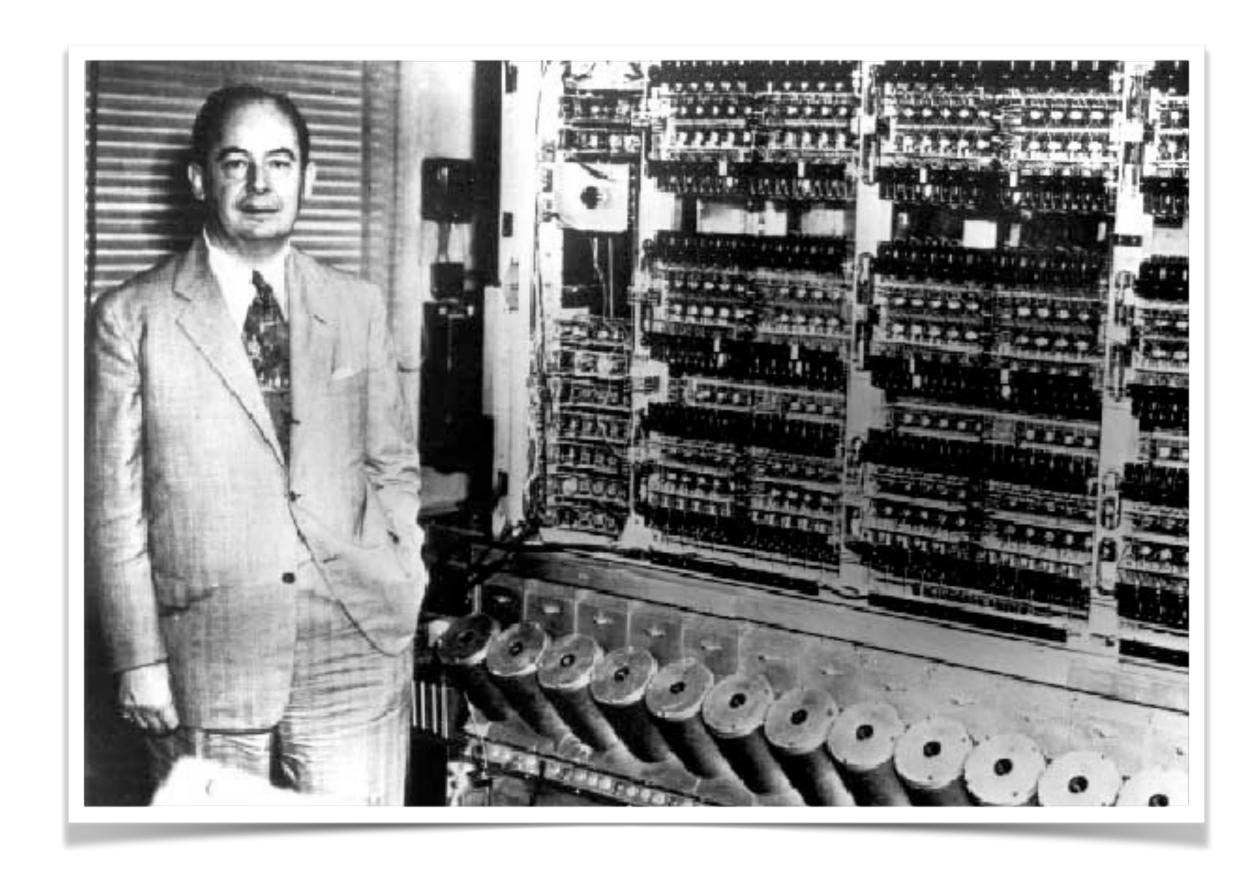

## 1939-40

the "bombe" was an electromechanical device designed by Alan Turing to decipher German Enigma-encrypted messages

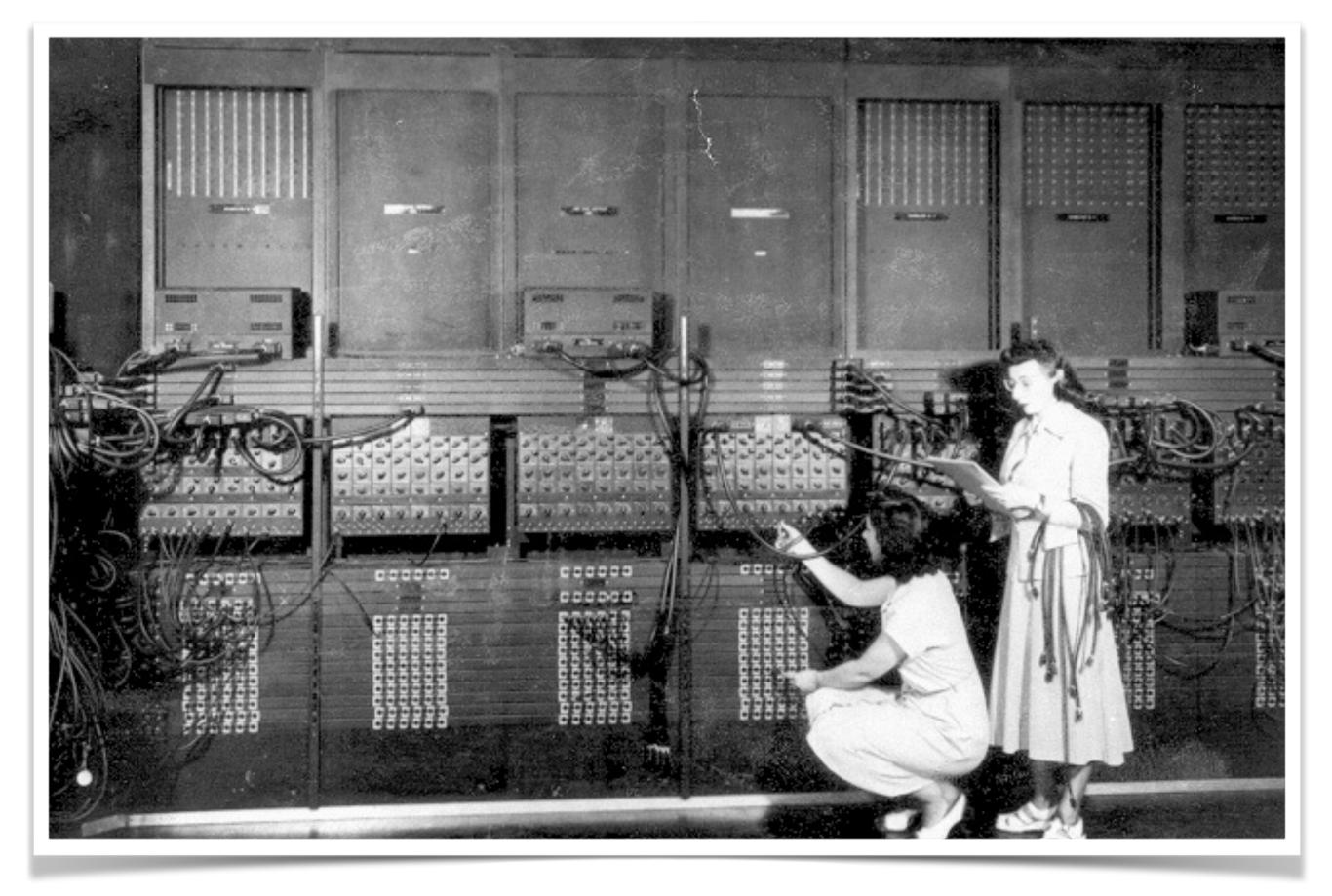

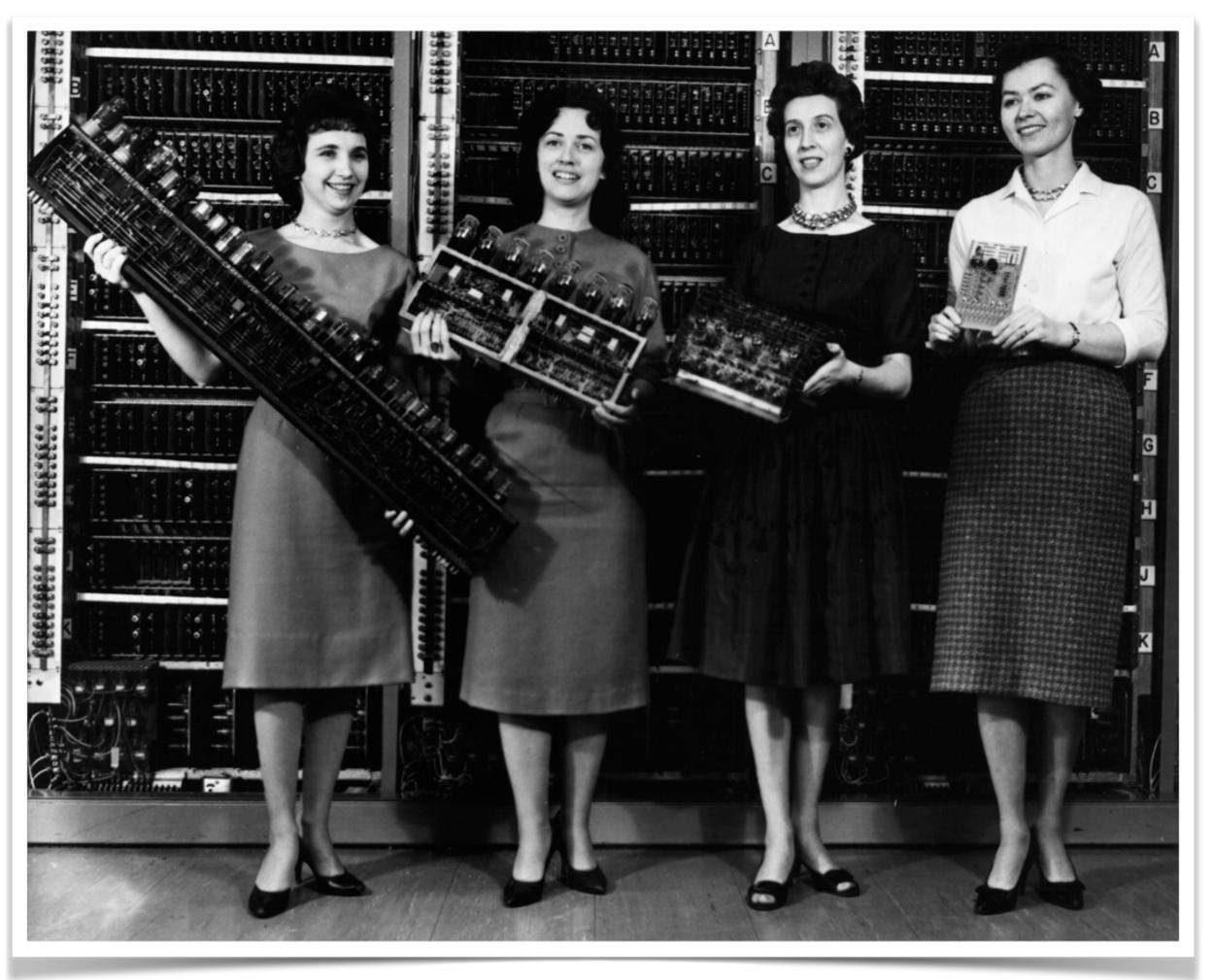

## 1943

the ENIAC was the first general electronic computer programs were hard-wired (dials & switches)

## 1944

the EDVAC is the first computer to rely on programs stored in memory

# 1945

John von Neumann describes the concept of programs stored in memory in a report about the EDVAC computer: the Von Neumann architecture

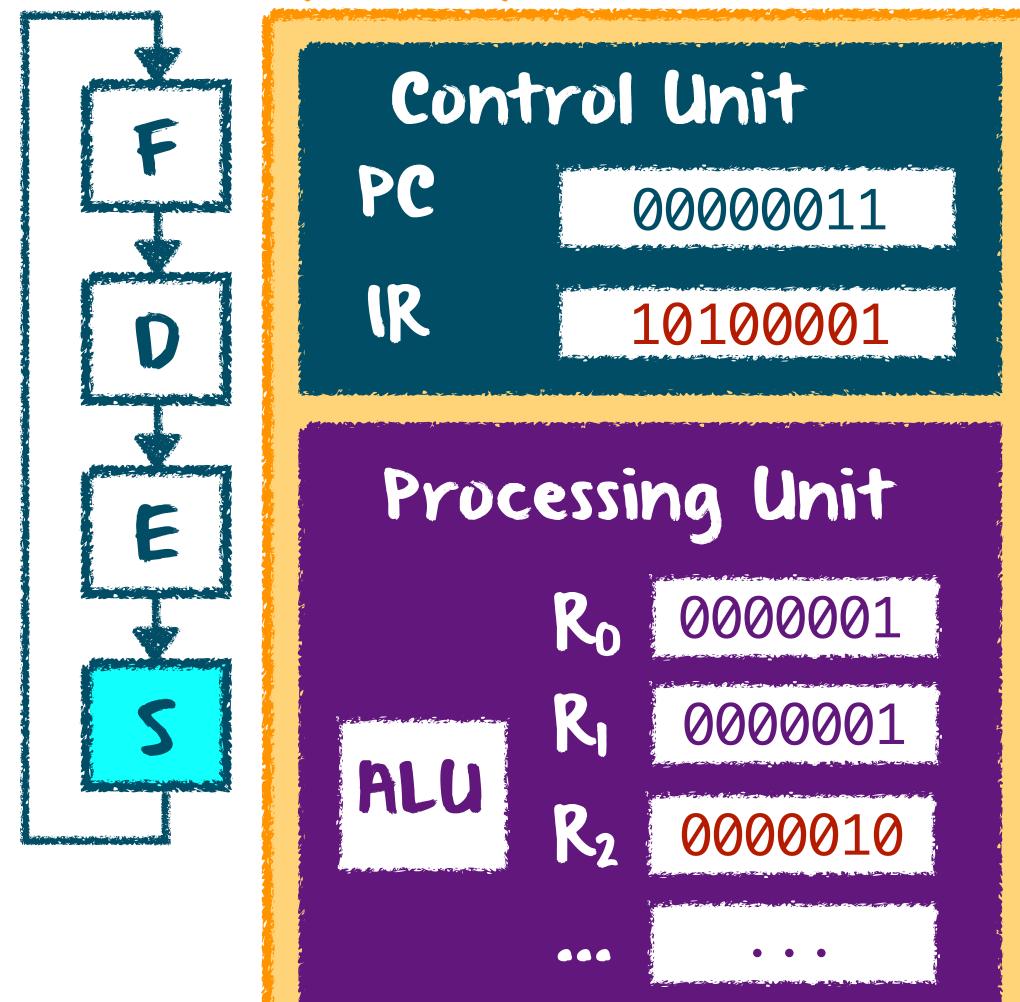

# the von Neumann model

PROCESSOR

Control Unit

PC 00000010

IR 01001011

PC: Program Counter IR: Instruction Register R<sub>0</sub>-R<sub>n-I</sub>: Register

# Processing Unit R<sub>0</sub> 0000001 R<sub>1</sub> 0000001 R<sub>2</sub> 00000000

ALU: Arithmetic & Logic Unit

MEMORY

000000000 10110110

00000001 00100100

00000010 10100001

00000011 ...

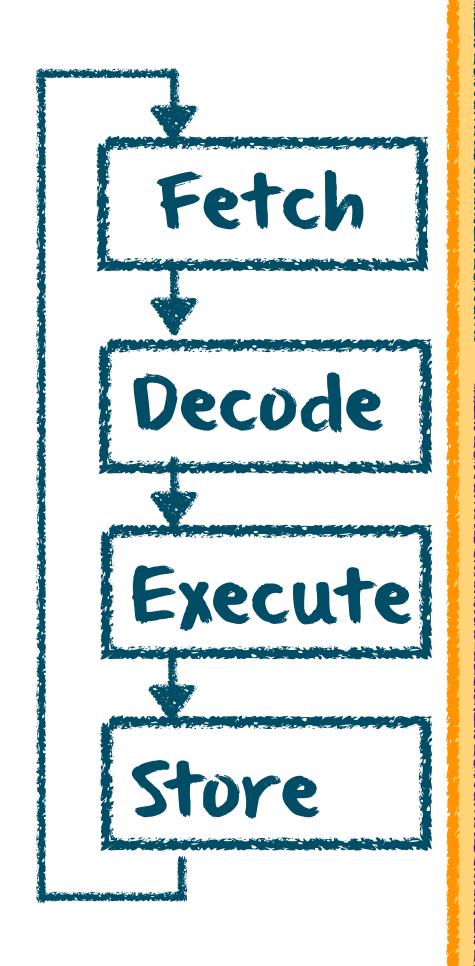

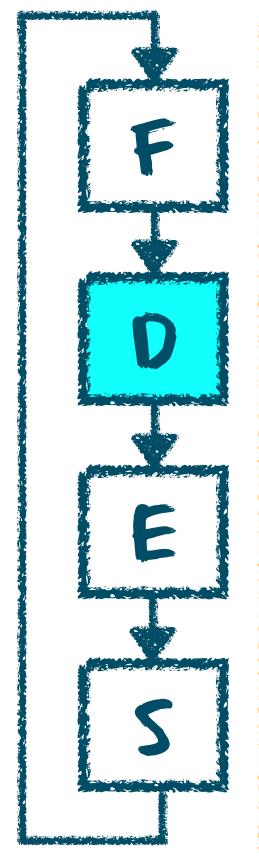

# fetch instruction

PROCESSOR

Control Unit PC IR Processing Unit ALU

3 PC + PC + 1 MEMORY

# fetch instruction

PROCESSOR

Control Unit

PC 00000011

IR 10100001

Processing Unit

R<sub>0</sub> 0000001

ALU

0000001

3 0000000

• • • •

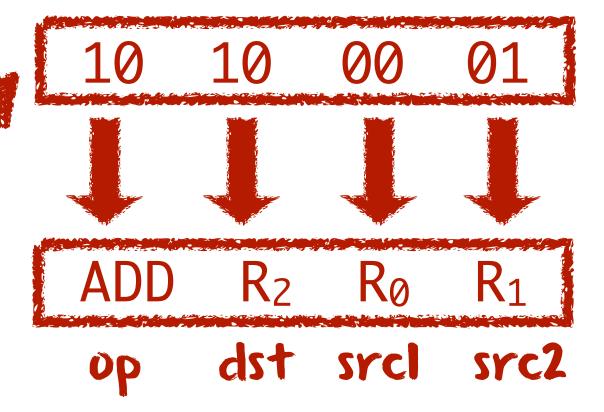

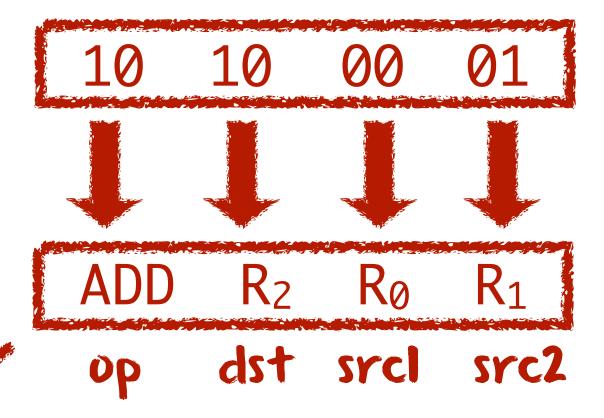

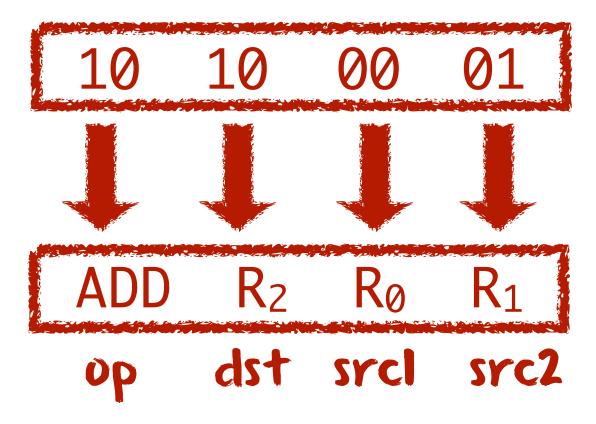

10 10 00 01

MEMORY

0000000 10110110

0000001 00100100

00000010 10100001

00000011

# decode instruction

PROCESSOR

#### Control Unit

PC 00000011

IR 10100001

#### Processing Unit

R<sub>0</sub> 0000001

R<sub>1</sub> 0000001

3 0000000

• • •

#### MEMORY

000000000

10110110

00000001

00100100

10100001

00000011

...

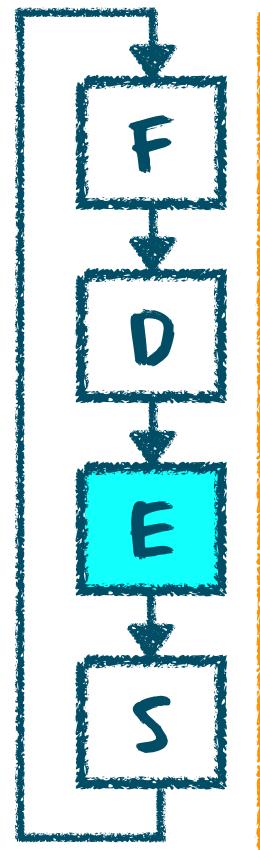

# execute instruction

PROCESSOR

#### Control Unit

PC 00000011

IR 10100001

#### Processing Unit

R<sub>0</sub> 0000001

R<sub>I</sub> 000001

R<sub>2</sub> 0000000

• • • •

#### MEMORY

000000000

10110110

00000001

00100100

10100001

00000011

...

# store result

PROCESSOR

# MEMORY 000000000 10110110 00000001 00100100 00000010 10100001 00000011

# instruction sets

#### ADDSD—Add Scalar Double-Precision Floating-Point Values

| Opcode      | Instruction          | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                        |

|-------------|----------------------|----------------|---------------------|------------------------------------------------------------------------------------|

| F2 0F 58 /r | ADDSD xmm1, xmm2/m64 | Valid          | Valid               | Add the low double-<br>precision floating-point<br>value from xmm2/m64 to<br>xmm1. |

#### **Description**

Adds the low double-precision floating-point values from the source operand (second operand) and the destination operand (first operand), and stores the double-precision floating-point result in the destination operand.

The source operand can be an XMM register or a 64-bit memory location. The destination operand is an XMM register. The high quadword of the destination operand remains unchanged. See Chapter 11 in the *Intel*® *64 and IA-32 Architectures Software Developer's Manual, Volume 1*, for an overview of a scalar double-precision floating-point operation.

In 64-bit mode, using a REX prefix in the form of REX.R permits this instruction to access additional registers (XMM8-XMM15).

#### Operation

DEST[63:0] ← DEST[63:0] + SRC[63:0]; (\* DEST[127:64] unchanged \*)

Intel IA-64 [2007]

Motorola 68000 [1980]

**ADD**

Add (M68000 Family) **ADD**

**Operation:** Source + Destination → Destination

Assembler ADD < ea > ,DnSyntax: ADD Dn, < ea >

**Attributes:** Size = (Byte, Word, Long)

**Description:** Adds the source operand to the destination operand using binary addition and stores the result in the destination location. The size of the operation may be specified as byte, word, or long. The mode of the instruction indicates which operand is the source and which is the destination, as well as the operand size.

#### **Condition Codes:**

| Χ | N | Z | V | С |  |  |

|---|---|---|---|---|--|--|

| * | * | * | * | * |  |  |

X — Set the same as the carry bit.

N — Set if the result is negative; cleared otherwise.

Z — Set if the result is zero; cleared otherwise.

V — Set if an overflow is generated; cleared otherwise.

C — Set if a carry is generated; cleared otherwise.

#### **Instruction Format:**

| 15       | 14  | 13 | 12 | 11       | 10 | 9      | 8      | 7                 | 6 | 5 | 4    | 3 | 2 | 1      | 0 |

|----------|-----|----|----|----------|----|--------|--------|-------------------|---|---|------|---|---|--------|---|

| 4        | 1 1 | 0  | 1  | DECICTED |    | ODMODE |        | EFFECTIVE ADDRESS |   |   |      |   |   |        |   |

| <u>'</u> |     |    |    | REGISTER |    |        | OPMODE |                   |   |   | MODE |   | R | EGISTE | R |